Компьютер обрабатывает сигналы параллельными потоками, поэтому ему легче «общаться» с параллельными, а не с последовательными внешними портами. В 1984 г. в составе IBM PC впервые появился параллельный порт. Задуман он был как средство подключения матричных принтеров, отсюда и название LPT - Line PrinTer или Line Printer Terminal. В дальнейшем для принтеров стали использовать быстродействующий интерфейс USB, а LPT-порт начал постепенно вытесняться из компьютерных спецификаций. Остряки сравнивают LPT с чемоданом без ручки - и выбросить жалко, и тащить невозможно. Тем не менее, «ветеран» ещё на многое способен, если, конечно, он присутствует в конкретном компьютере.

Разъём LPT-порта имеет 25 контактов. Нормой «де-факто» считается розетка DB-25F в компьютере и вилка DB-25M в ответном кабеле (Табл. 4.2). Нумерация контактов вилок и розеток зеркальная (Рис. 4.7, а, б).

Таблица 4.2. Раскладка сигналов в 25-контактном разъёме LPT-порта

|

Расшифровка |

Направление |

Вход/выход |

Вход/выход |

Подтверждение |

Готовность |

Нет бумаги |

Автоперенос |

Вход/выход |

Инициализация |

Вход/выход |

Выбор входа |

Вход/выход |

Рис. 4.7. Внешний вид спереди 25-контактных разъёмов LPT-порта: а) розетка DB-25F в компьютере; б) вилка DB-25M в соединительном кабеле.

Первоначально линии LPT-порта были однонаправленными SPP (Standard Parallel Port). Часть из них работала только на вход, часть - только на выход, что по набору сигналов и протоколу обмена соответствовало принтерному интерфейсу «Centronics». В 1994 г. был утверждён новый стандарт параллельного интерфейса IEEE 1284, предусматривающий двунаправленные линии и три режима работы: SPP, EPP (Enhanced Parallel Port), ECP (Extended Capabilities Port).

Уровни электрических сигналов LPT-порта совпадают с обычными «пятивольтовыми» логическими микросхемами. Раньше в компьютерах применялись буферные TTJl-микросхемы серии 74LSxx, позднее - КМОП-микросхемы и БИС, примерно эквивалентные серии 74ACxx. В последнем случае можно ориентировочно считать, что НИЗКИЙ уровень равен 0.1..0.2 В, а ВЫСОКИЙ - 4.5…4.9 В.

Стандартом регламентируется нагрузка 14 мА по каждому выходу при сохранении напряжения не менее +2.4 В ВЫСОКОГО и не более +0.4 В НИЗКОГО уровня. Однако в разных материнских платах выходные буферы LPT-порта могут иметь разную нагрузочную способность, в том числе и ниже стандарта («слабый» порт).

Требования к соединительным кабелям, подключаемым к LPT-порту:

Сигнальные провода должны быть свиты в пары с общим проводом GND;

Каждая пара должна иметь импеданс 56…68 Ом в диапазоне частот 4… 16 M Гц;

Если применяется плоский ленточный кабель, то сигнальные провода должны физически чередоваться с общим проводом GND (локальные экраны);

Уровень перекрёстных помех между сигналами не более 10%;

Кабель должен иметь экран, покрывающий не менее 85% внешней поверхности. На концах кабеля экран должен быть окольцован и соединён с «земляным» контактом разъёма;

В разъёме кабеля можно запаять на контакты 1…17 последовательные резисторы C2-23 (OMJIT-O.125) сопротивлением 100…300 Ом (Рис. 4.8). Это позволит защитить компьютер от случайных коротких замыканий в нагрузке и уменьшить высокочастотный «звон» на фронтах сигналов.

Рис. 4.8. Электрическая схема LPT-кабеля с «антизвонными» резисторами.

Схемы соединения MK с LPT-портом можно разделить на три группы:

Приём сигналов от компьютера (Рис. 4.9, а…з);

Передача сигналов в компьютер (Рис. 4.10, а…д);

Приём/передача сигналов одновременно (Рис. 4.11, a…e).

В схемах приняты некоторые упрощения. В качестве входного сигнала указывается в основном «DO», а в качестве выходного - «АСК», хотя могут быть и другие, перечисленные в Табл. 4.2. На каждом конкретном компьютере работоспособность самодельных схем необходимо проверять экспериментально, что связано с наличием «сильных» и «слабых» LPT-портов по нагрузочной способности.

Рис. 4.9. Схемы ввода сигналов из LPT-порта в MK (начало):

а) резистор R1 ограничивает входной ток. Элементы R2, C1 могут отсутствовать, но они уменьшают «звон» на фронтах сигналов при длинном кабеле;

б) буферный транзистор VT1 инвертирует сигнал. Диод VD1 не обязателен, но он защищает транзистор от ошибочной подачи большого отрицательного напряжения. Если не ставить резистор R2, то схема останется работоспособной, однако при отстыковке кабеля от LPT-порта возможны ложные срабатывания транзистора VT1 от внешних помех и наводок;

в) диод VD1 отсекает помехи и повышает порог срабатывания транзистора VT1. Резистор R1 надёжно закрываеттранзистор VT1 при НИЗКОМ уровне с LPT-порта;

г) буферный логический элемент DD1 имеет выход с открытым коллектором. Фронты сигналов формируются элементами R1, C1. Можно вместо инвертора DD1 поставить повторитель К155ЛП9, сделав соответствующие изменения в программе MK и компьютера;

д) триггер Шмитта DD1 (замена - К555ТЛ2) повышает помехоустойчивость. Чем меньше сопротивление резисторов R1, R2, тем больше крутизна фронтов сигнала. При отключённом кабеле от LPT-порта резистор R1 не даёт входу микросхемы DD1 «висеть в воздухе»;

е) последовательное включение двух логических элементов DD11, /)/)/.2увеличивает (восстанавливает) крутизну фронтов сигнала. Резистор R1 устраняет выбросы, «звон»;

Рис. 4.9. Схемы ввода сигналов из LPT-порта в MK (окончание):

ж) данные, поступающие от LPT-порта, предварительно помещаются в промежуточный регистр DD1. Запись производится при ВЫСОКОМ уровне на входе «С» микросхемы DD1, хранение - при НИЗКОМ. Такое решение устраняет помехи, поскольку в LPT-порт в зависимости от установленных в компьютере драйверов периодически могут выводиться случайные данные. Их устраняют программно, например, путём многократного считывания входного сигнала с линий MK;

з) буферизация LPT-порта мощными транзисторными ключами, находящимися в микросхеме DA1 фирмы Texas Instruments. Резисторы R1…R8 могут иметь в 10… 15 раз более низкие сопротивления, что позволяет подключить параллельно выходам микросхемы А4/другие узлы устройства.

Рис. 4.10. Схемы вывода сигналов из MK в LPT-порт (начало):

а) непосредственное подключение выхода MK без буферных элементов. Резисторы R1, R2 уменьшают отражение сигналов в линии. Кроме того, резистор R2 защищает выход MK от случайного короткого замыкания с цепью GND в проводах соединительного кабеля;

б) триггер Шмитта DD1 служит защитным буфером для MK при аварийной ситуации на выходе (короткое замыкание или подача большого напряжения);

в) микросхема DD1 имеет выход с открытым коллектором, что защищает её от короткого замыкания в проводах и разъёмах соединительного кабеля;

г) подача двух противофазных сигналов в компьютер. Цель - программная необходимость или организация дублирующего (контрольного) канала передачи данных;

д) опторазвязка на элементах HL1, BL1, которые применяются в компьютерных механических «мышах». Транзистор КГ/усиливает и инвертирует сигнал. Для нормальной работы устройства компьютер должен выставить ВЫСОКИЙ уровень на линии «D8».

Рис. 4.11. Комбинированные схемы ввода/вывода сигналов между MK и LPT-портом (начало):

а) если компьютер выставляет на линии «DO» ВЫСОКИЙ уровень, то MK в режиме выхода может генерировать сигнал «АСК» через резистор R1. Если MK переводится в режим входа, то компьютер может передавать ему данные по линии «DO» через диод VD1 при этом внутренний « pull-up» резистор MK формирует ВЫСОКИЙ уровень;

б) сигнал от LPT-порта вводится в MK через инвертор на транзисторе VT1 при этом компьютер должен выставить ВЫСОКИЙ уровень на линии «D2». Информация в MK вводится с линии «DO» через резистор R1 Высокое сопротивление резистора R1 физически развязывает входной и выходной каналы;

Рис. 4.11. Комбинированные схемы ввода/вывода сигналов между MK и LPT-портом (окончание):

б) сигнал от LPT-порта вводится в MK через инвертор на транзисторе VT1, при этом компьютер должен выставить НИЗКИЙ уровень на линии «DO». Информация в МК вводится через элементы R1, R3, VT2;

г) сигнал от LPT-порта вводится в MK через повторитель на транзисторе VT1, при этом компьютер должен выставить ВЫСОКИЙ уровень на линии «DO». Информация в MK вводится через повторитель на микросхеме DD1\

ж) сигналы «D0»…«D3» вводятся в MK при НИЗКОМ уровне на линии «INIT», при этом компьютер должен настроить линии «D4»…«D7» как входы. В настройках BIOS компьютера надо установить двунаправленный режим EPP или ЕСР для LPT-порта. Информация в компьютер из МК передаётся по линиям «D4»…«D7» при ВЫСОКОМ уровне на линии «INIT». Резистор R1 переводит выходы микросхемы DD1 в Z-состояние при отключённом кабеле от LPT-порта;

e) сигнал от MK в LPT-порт вводится через повторитель DD1.2, при этом компьютер должен выставить ВЫСОКИЙ уровень на линии «D2» и НИЗКИЙ уровень на линии «D5». Информация в MK вводится через повторитель DD1.1 при НИЗКОМ уровне налинии «D2». Стробирование сигналов по входам «Е1», «Е2» микросхемы DD1 повышает достоверность передачи данных.

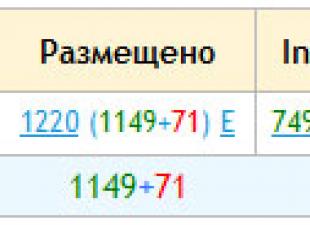

За время существования этого сайта мне довольно часто задают один и тот же вопрос, который можно описать примерно следующим образом:

В итоге решил описать этот вопрос подробнее и написать статью. Да, действительно, сейчас стационарных PC с LPT портом нужно поискать (т.е. далеко не каждая "мать" сейчас идет в комплекте с LPT портом). Про ноутбуки вообще говорить не приходится. Современные модели LPT порт вообще не применяют. Только очень дорогие и специализированные машины, типа DELL, могут "похвастаться" наличием этого порта.

Также, сейчас в продаже можно свободно приобрести вот такие устройства, называемые LPT-USB переходниками.

Инстркуция гласит что этот прибор полностью совместим с различными принтерами, сканерами и т.д. Подключаем переходник к USB порту, устанавливаем драйвера. Смотрим диспетчер устройств. Скорее всего в ветке "Порты LPT/COM" ни чего не появилось (хотя бывают исключения). Скорее всего повится либо новая ветка со странным устройством с именем, например, LPT1USB либо в разделе USB устройств появится странная запись о "USB устройстве поддержки LPT принтеров" . Пробуем запустить какой-нибудь пример из статей выше. И ни тут то было - ни чего не работает. Пробуем адрес порта LPT1 - ни чего не работает. Пробуем адресс порта LPT2. К сожалению, такая модернизация адреса в запросах тоже ни к чему не приводит - светодиоды как не загорались так и не загораются.

Чтобы разобраться в чем тут дело давайте вернемся на время к обычному "родному железному" LPT порту - LPT1, который из материнской платы "торчит". Зайдем в диспетчер устройств, заглянем в свойства нашего порта. Там мы увидим вот такую картину. Отлично видно, что система прописала базовый адрес ввода-вывода 0x378 и запрос на прерывание номер 7. Все правильно.

Теперь погрузимся на уровень программирования. В примерах статей выше мы минуя систему защиты ввода-вывода легальными и нелегальными способами напрямую общались с реально существующим регистром ввода-вывода, которому присвоен адрес 0x378. Тут все понятно. Незабудем также о том, что Windows рекомендует работать с LPT портом используя вызовы API функций - OpenFile(), WriteFile(), ReadFile() . Приложения, которые используют LPT порт для обмена информацией по парралельному интерфейсу с внешними устройствами (принтер, например) так и делает. У него нет задачи установить на каком-либо бите регистра Data лигическую еденицу. Ему (приложению) нужно просто отправить пакет данных, а кто там будет какие линиии при этом "дергать" и считывать его не сильно интересует. Эти операции проводит системный драйвер LPT порта. Он подгружается в память при загрузке ОС. Когда мы вызываем функцию OpenFile("LPT1", ....) мы по сути дела обращаемся к драйверу порта, который имеет символическое имя LPT1. Драйвер делает кучу всякой работы - запрещает доступ к порту другим процессам, настраивает параметры протокола передачи данных, собственно реализует эту передачу, но в конечном итоге все это сводится к прямому управлению отдельными битами LPT порта на уровне ядра ОС.

А теперь попробуем поработать с нашим переходником USB-LPT. Начнем как не покажется странным, с API вызовов. Запускаем OpenFile("LPT1USB", ...) (смотря как этот переходник диспетчере устройств назовется, если вообще назовется). Что при этом происходит? Дело в том, что теперь мы будем работать не с драйвером LPT порта ОС а с драйвером этого переходника! Вот в чем фокус то! Он принимает пакет данных от нашего пользовательского приложения и в нужном формате через систмный драйвер USB отсылает этот пакет на USB контроллер, "ноги" которого торчат из внешней LPT розетки на проводе (ну это так, "грубое объяснение"). Видете, здесь нет ни какого намека на обращение к регистрам по адресам 0x378(0x278), т.к. их просто нет!

Поэтому, когда Вы патаетесь запускать примеры данного раздела и обращаться напрямую по адресам 0x378 (если этот "псевдо порт" назвался LPT1USB или что-то в этом духе), 0x278 (LPT2_...) и т.д. ни чего не происходит. Их просто нет! А вот программа котороая работает через API вызовы ни чего не заметит - вся низкоуровневая работа делается драйвером, а каким драйвером и куда пойдут пакеты данных (в реальный порт ввода-вывода или в USB хост-контроллер) - приложению неважно! Попробуйте открыть свойства "псевдопорта" в диспетчере устройств. Нет вкладки с ресурсами? Есть, но там каие-то неадекватные значения или вкладка деактивировнна? В том то и дело.

Почему 99%? Потомоу что есть самодельниые USB-LPT переходники, которые определяются Windows как полноценный порт LPT1 и ему присваивается вполне обыденный адрес 0x378. Обращения на прямую к пинам порта проходят успешно! Однако это очень нестандартная конструкция (в первую очередь драйвер, который занимается перехватом обращений по базовому адресау порта LPT1). Все это не очень надежно (обновление ОС - и конструкция теряет работоспосбность) и для использования рекомендовано быть может только с натяжкой.

Как ни покажется странным - решение ЕСТЬ. Вы всегда сможете добавить настоящий LPT порт в свой настольный компьютер или ноутбук. Во-первых, забудте сразу о переходниках с интерфейсом USB. Для решения этой задачи необходимо приробрести PCI-LPT переходник для настольного PC (необходимо наличие свободного PCI слота) или PCMCIA-LPT переходник для ноутбука (см. фото ниже).

|

|

|

В случае использования этих устройств ни каких проблем нет. Определяются они как настоящие "родные" LPT порты. Соответствующая запись будет добавлена в диспетчер устройств во вклдаку "LPT/COM порты" . Прямое обращение к пинам порта будет работать.

Параллельные интерфейсы характеризуются тем, что в них для передачи бит в слове используются отдельные сигнальные линии, и биты передаются одновременно. Параллельные интерфейсы используют логические уровни ТТЛ (транзисторно-транзисторной логики), что ограничивает длину кабеля из-за невысокой помехозащищенности ТТЛ-интерфейса. Гальваническая развязка отсутствует. Параллельные интерфейсы используют для подключения принтеров. Передача данных может быть как однонаправленной (Centronics), так и двунаправленной (Bitronics). Иногда параллельный интерфейс используют для связи между двумя компьютерами - получается сеть, "сделанная на коленке" (LapLink). Ниже будут рассмотрены протоколы интерфейсов Centronics, стандарт IEEE 1284, а также реализующие их порты PC.

1.1. Интерфейс Centronics и LPT-порт

Для подключения принтера по интерфейсу Centronics в PC был введен порт параллельного интерфейса - так возникло название LPT-порт (Line PrinTer - построчный принтер). Хотя сейчас через этот порт подключаются не только построчные принтеры, название "LPT" осталось.

1.1.1. Интерфейс Centronics

Понятие Centronics относится как к набору сигналов и протоколу взаимодействия, так и к 36-контактному разъему на принтерах. Назначение сигналов приведено в табл. 1.1, а временные диаграммы обмена с принтером - на рис. 1.1.

Интерфейс Centronics поддерживается принтерами с параллельным интерфейсом. Его отечественным аналогом является интерфейс ИРПР-М.

Традиционный, он же стандартный, LPT-порт SPP (Standard Parallel Port) является однонаправленным портом, через который программно реализуется протокол обмена Centronics. Порт вырабатывает аппаратное прерывание по импульсу на входе Ack#. Сигналы порта выводятся на разъем DB-25S (розетка), установленный непосредственно на плате адаптера (или системной плате) или соединяемый с ней плоским шлейфом. Название и назначение сигналов разъема порта (табл. 1.2) соответствуют интерфейсу Centronics.

| Сигнал | I/O* | Контакт | Назначение |

| Strobe# | I | 1 | Строб данных. Данные фиксируются по низкому уровню сигнала |

| Data | I | 2-9 | Линии данных. Data 0 (контакт 2) - младший бит |

| Ack# | O | 10 | Acknowledge - импульс подтверждения приема байта (запрос на прием следующего). Может использоваться для формирования запроса прерывания |

| Busy | O | 11 | Занято. Прием данных возможен только при низком уровне сигнала |

| PaperEnd | O | 12 | Высокий уровень сигнализирует о конце бумаги |

| Select | O | 13 | Сигнализирует о включении принтера (обычно в принтере соединяется резистором с цепью +5 В) |

| AutoLF# | I | 14 | Автоматический перевод строки. При низком уровне принтер, получив символ CR (Carriage Return - возврат каретки), автоматически выполняет и функцию Lf (Line Feed - перевод строки) |

| Error# | O | 32 | Ошибка: конец бумаги, состояние OFF-Line или внутренняя ошибка принтера |

| Init# | I | 31 | Инициализация (сброс в режим параметров умолчания, возврат к началу строки) |

| Select ln# | I | 36 | Выбор принтера (низким уровнем). При высоком уровне принтер не воспринимает остальные сигналы интерфейса |

| GND | - | 19-30, 33 | Общий провод интерфейса |

Рис. 1.1. Передача данных по протоколу Centronics

| Контакт DB-25S | Номер провода в кабеле | Назначение | ||

| I/O* | Reg. Bit** | Сигнал | ||

| 1 | 1 | O/I | CR.0\ | Strobe# |

| 2 | 3 | O(I) | DR.0 | Data 0 |

| 3 | 5 | O(I) | DR.1 | Data 1 |

| 4 | 7 | O(I) | DR.2 | Data 2 |

| 5 | 9 | O(I) | DR.3 | Data 3 |

| 6 | 11 | O(I) | DR.4 | Data 4 |

| 7 | 13 | O(I) | DR.5 | Data 5 |

| 8 | 15 | O(I) | DR.6 | Data 6 |

| 9 | 17 | O(I) | DR.7 | Data 7 |

| 10 | 19 | I*** | SR.6 | Ack# |

| 11 | 21 | I | SR.7 | Busy |

| 12 | 23 | I | SR.5 | PaperEnd (PE) |

| 13 | 25 | I | SR.4 | Select |

| 14 | 2 | O/I | CR.1\ | Auto LF# |

| 15 | 4 | I | SR.3 | Error* |

| 16 | 6 | O/I | CR.2 | Init# |

| 17 | 8 | O/I | CR.3\ | Select ln# |

| 18-25 | 10, 12, 14, 16, 18, 20, 22, 24, 26 | - | - | - |

** Символом "\" отмечены инвертированные сигналы (1 в регистре соответствует низкому уровню линии).

*** Вход Ack# соединен резистором (10 кОм) с питанием +5 В.

1.1.2. Традиционный LPT-порт

Адаптер параллельного интерфейса представляет собой набор регистров, расположенных в пространстве ввода/вывода. Регистры порта адресуются относительно базового адреса порта, стандартными значениями которого являются 3BCh, 378h и 278h. Порт может использовать линию запроса аппаратного прерывания, обычно IRQ7 или IRQ5 . Порт имеет внешнюю 8-битную шину данных, 5-битную шину сигналов состояния и 4-битную шину управляющих сигналов,

BIOS поддерживает до четырех (иногда до трех) LPT-портов (LPT1-LPT4) своим сервисом - прерыванием INT 17h , обеспечивающим через них связь с принтером по интерфейсу Centronics . Этим сервисом BIOS осуществляет вывод символа (по опросу готовности, не используя аппаратных прерываний), инициализацию интерфейса и принтера, а также опрос состояния принтера.

Стандартный порт имеет три 8-битных регистра, расположенных по соседним адресам в пространстве ввода/вывода, начиная с базового адреса порта BASE (3BCh, 378h или 278h).

Data Register (DR) - регистр данных, адрес=ВASЕ. Данные, записанные в этот порт, выводятся на выходные линии интерфейса DATA. Данные, считанные из этого регистра, в зависимости от схемотехники адаптера соответствуют либо ранее записанным данным, либо сигналам на тех же линиях, что не всегда одно и то же. Если в порт записать байт с единицами во всех разрядах, а на выходные линии интерфейса через микросхемы с выходом типа "открытый коллектор" подать какой-либо код (или соединить ключами какие-то провода со схемной землей), то этот код может быть считан из того же регистра данных. Таким образом на многих старых моделях адаптеров можно реализовать порт ввода дискретных сигналов, однако выходным цепям передатчика информации придется "бороться" с выходным током логической единицы выходных буферов адаптера. Схемотехника ТТЛ такие решения не запрещает, но если внешнее устройство выполнено на , их выходного тока может не хватить для формирования логического 0. Однако современные адаптеры часто имеют в выходной цепи согласующий резистор с сопротивлением до 50 Ом. Выходной ток короткого замыкания выхода на землю обычно не превышает 30 мА. Простой расчет показывает, что в случае короткого замыкания контакта разъема на землю при выводе "единицы" на этом падает напряжение 1,5 В, что входной схемой приемника будет воспринято как "единица". Так что такой способ ввода не будет работать на всех компьютерах.

На некоторых адаптерах портов выходной буфер отключается перемычкой на плате. Тогда порт превращается в обыкновенный порт ввода.

Status Register (SR) - регистр состояния; представляет собой 5-битный порт ввода сигналов состояния принтера (биты SR.4-SR.7), адрес==BASE+1. Бит SR. 7 инвертируется - низкому уровню сигнала соответствует единичное значение бита в регистре, и наоборот.

Назначение бит регистра состояния (в скобках даны номера контактов разъема):

- SR.7 - Busy - инверсные отображения состояния линии Busy (11): при низком уровне на линии устанавливается единичное значения бита - разрешение на вывод очередного байта.

- SR.6 - Ack (Acknowledge) - отображения состояния линии Ack# (10).

- SR.5 - РЕ (Paper End) - отображения состояния линии Paper End (12). Единичное значение соответствует высокому уровню линии - сигналу о конце бумаги в принтере.

- SR.4 - Select - отображения состояния линии Select (13). Единичное значение соответствует высокому уровню линии - сигналу о включении принтера.

- SR.3 - Error - отображения состояния линии Error (15). Нулевое значение соответствует низкому уровню линии - сигналу о любой ошибке принтера.

- SR.2 - PIRQ - флаг прерывания по сигналу Ack# (только для порта PS/2). Бит обнуляется, если сигнал Ack# вызвал аппаратное прерывание. Единичное значение устанавливается по аппаратному сбросу и после чтения регистра состояния.

- SR - зарезервированы.

Control Register (CR) - регистр управления, адрес=BASE+2. Как и регистр данных, этот 4-битный порт вывода допускает запись и чтение (биты 0-3), но его выходной буфер обычно имеет тип "открытый коллектор". Это позволяет корректно использовать линии данного регистра как входные при программировании их в высокий уровень. Биты 0, 1, 3 инвертируются.

Назначение бит регистра управления:

- CR - зарезервированы.

- CR.5 - Direction - бит управления направлением передачи (только для портов PS/2). Запись единицы переводит порт данных в режим ввода. При чтении состояние бита не определено.

- CR.4 - AcklntEn (Ack Interrupt Enable) - единичное значение разрешает прерывание по спаду сигнала на линии Ack# - сигнал запроса следующего байта.

- CR.3 - Select ln - единичное значение бита соответствует низкому уровню на выходе Select ln# (17) - сигналу, разрешающему работу принтера по интерфейсу Centronics.

- CR.2 - Init - нулевое значение бита соответствует низкому уровню на выходе Init# (16) - сигналу аппаратного сброса принтера.

- CR.1 - Auto LF - единичное значение бита соответствует низкому уровню на выходе Auto LF# (14) - сигналу на автоматический перевод строки (LF - Line Feed) по приему байта возврата каретки (CR). Иногда сигнал и бит называют AutoFD или AutoFDXT.

- CR.0 - Strobe - единичное значение бита соответствует низкому уровню на выходе Strobe# (1) - сигналу стробирования выходных данных.

Запрос аппаратного прерывания (обычно IRQ7 или IRQ5) вырабатывается по отрицательному перепаду сигнала на выводе 10 разъема интерфейса (Ack#) при установке CR.4=1. Во избежание ложных прерываний контакт 10 соединен резистором с шиной +5 В. Прерывание вырабатывается, когда принтер подтверждает прием предыдущего байта. Как уже было сказано, BIOS это прерывание не использует и не обслуживает.

Процедура вывода байта по интерфейсу Centronics включает следующие шаги (в скобках приведено требуемое количество шинных операций процессора):

- Вывод байта в регистр данных (1 цикл IOWR#).

- Ввод из регистра состояния и проверка готовности устройства (бит SR.7 - сигнал Busy). Этот шаг зацикливается до получения готовности или до срабатывания программного тайм-аута (минимум 1 цикл IORD#).

- По получении готовности выводом в регистр управления устанавливается строб данных, а следующим выводом строб снимается (2 цикла IOWR#). Обычно, чтобы переключить только один бит (строб), регистр управления предварительно считывается, что добавляет еще один цикл IORD#.

Видно, что для вывода одного байта требуется 4-5 операций ввода/вывода с регистрами порта (в лучшем случае, когда готовность обнаружена по первому чтению регистра состояния). Отсюда вытекает главный недостаток вывода через стандартный порт - невысокая скорость обмена при значительной загрузке процессора. Порт удается разогнать до скоростей 100-150 Кбайт/с при полной загрузке процессора, что недостаточно для печати на лазерном принтере. Другой недостаток - функциональный - сложность использования в качестве порта ввода.

Стандартный порт асимметричен - при наличии 12 линий (и бит), нормально работающих на вывод, на ввод работают только 5 линий состояния. Если необходима симметричная двунаправленная связь, на всех стандартных портах работоспособен режим полубайтного обмена - Nibble Mode. В этом режиме, называемом также Hewlett Packard Bitronics, одновременно передаются 4 бита данных, пятая линия используется для квитирования. Таким образом, каждый байт передается за два цикла, а каждый цикл требует по крайней мере 5 операций ввода/вывода.

1.1.3. Расширения параллельного порта

Недостатки стандартного порта частично устраняли новые типы портов, появившиеся в компьютерах PS/2.

Двунаправленный порт 1 (Type 1 parallel port) -интерфейс, введенный в PS/2. Такой порт кроме стандартного режима может работать в режиме ввода или двунаправленном режиме. Протокол обмена формируется программно, а для указания направления передачи в регистр управления порта введен специальный бит CR.5:0 - буфер данных работает на вывод, 1 - на ввод. Не путайте этот порт, называемый также enhanced bidirectional, с ЕРР. Данный тип порта прижился и в обычных компьютерах.

Порт с прямым доступом к памяти (Type 3 DMA parallelport) применялся в PS/2 моделей 57, 90, 95. Был введен для повышения пропускной способности и разгрузки процессора при выводе на принтер. Программе, работающей с портом, требовалось только задать в памяти блок данных, подлежащих выводу, а затем вывод по протоколу Centronics производился без участия процессора.

Позже появились другие адаптеры LPT-портов, реализующие протокол обмена Centronics аппаратно - Fast Centronics. Некоторые из них использовали FIFO-буфер данных - Parallel Port FIFO Mode. He будучи стандартизованными, такие порты разных производителей требовали использования собственных специальных драйверов. Программы, использующие прямое управление регистрами стандартных портов, не умели более эффективно их использовать. Такие порты часто входили в состав мультикарт VLB. Существуют их варианты с шиной ISA, в том числе встроенные.

1.2. Стандарт IEEE 1284

Стандарт на параллельный интерфейс IEEE 1284, принятый в 1994 году, определяет порты SPP, ЕРР и ЕСР. Стандарт определяет 5 режимов обмена данными, метод согласования режима, физический и электрический интерфейсы. Согласно IEEE 1284, возможны следующие режимы обмена данными через параллельный порт:

- Режим совместимости (Compatibility Mode) - однонаправленный (вывод) по протоколу Centronics. Этот режим соответствует стандартному порту SPP.

- Полубайтный режим (Nibble Mode) - ввод байта в два цикла (по 4 бита), используя для приема линии состояния. Этот режим обмена может использоваться на любых адаптерах.

- Байтный режим (Byte Mode) - ввод байта целиком, используя для приема линии данных. Этот режим работает только на портах, допускающих чтение выходных данных (Bi-Directional или PS/2 Type 1).

- Режим ЕРР (Enhanced Parallel Port) (EPP Mode) - двунаправленный обмен данными. Управляющие сигналы интерфейса генерируются аппаратно во время цикла обращения к порту. Эффективен при работе с устройствами внешней памяти и адаптерами локальных сетей.

- Режим ЕСР (Extended Capability Port) (ECP Mode) - двунаправленный обмен данными с возможностью аппаратного сжатия данных по методу RLE (Run Length Encoding) и использования FIFO-буферов и DMA. Управляющие сигналы интерфейса генерируются аппаратно. Эффективен для принтеров и сканеров.

В компьютерах с LPT-портом на системной плате режим - SPP, ЕРР, ЕСР или их комбинация - задается в BIOS Setup. Режим совместимости полностью соответствует стандартному порту SPP. Остальные режимы подробно рассмотрены ниже.

1.2.1. Физический и электрический интерфейсы

Стандарт IEEE 1284 определяет физические характеристики приемников и передатчиков сигналов. Спецификации стандартного порта не задавали типов выходных схем, предельных значений величин нагрузочных резисторов и емкости, вносимой цепями и проводниками. На относительно невысоких скоростях обмена разброс этих параметров не вызывал проблем совместимости. Однако расширенные (функционально и по скорости передачи) режимы

требуют четких спецификаций. IEEE 1284 определяет два уровня интерфейсной совместимости. Первый уровень (Level I) определен для устройств медленных, но использующих смену направления передачи данных. Второй уровень (Level II) определен для устройств, работающих в расширенных режимах, с высокими скоростями и длинными кабелями. К передатчикам предъявляются следующие требования:

- Уровни сигналов без нагрузки не должны выходить за пределы -0,5... +5,5 В.

- Уровни сигналов при токе нагрузки 14 мА должны быть не ниже +2,4 В для высокого уровня (Vон) и не выше +0,4 В для низкого уровня (Vol) на постоянном токе.

- Выходной импеданс Ro, измеренный на разъеме, должен составлять 50±5 Ом на уровне Voh~Vol. Для обеспечения заданного импеданса используют последовательные резисторы в выходных цепях передатчика. Согласование импеданса передатчика и кабеля снижает уровень импульсных помех.

- Скорость нарастания (спада) импульса должна находиться в пределах 0,05-0,4 В/нс.

Требования к приемникам:

- Допустимые пиковые значения сигналов -2,0...+7,0 В.

- Пороги срабатывания должны быть не выше 2,0 В (Vh) для высокого уровня и не ниже 0,8 В (Vl) для низкого.

- Приемник должен иметь гистерезис в пределах 0,2...1,2 В (гистерезисом обладают специальные микросхемы — ).

- Входной ток микросхемы (втекающий и вытекающий) не должен превышать 20 мкА, входные линии соединяются с шиной питания +5 В резистором 1,2 кОм.

- Входная емкость не должна превышать 50 пФ.

Когда появилась спецификация ЕСР, фирма Microsoft рекомендовала применение динамических терминаторов на каждую линию интерфейса. Однако в настоящее время следуют спецификации IEEE 1284, в которой динамические терминаторы не применяются. Рекомендованные схемы входных, выходных и двунаправленных цепей приведены на рис. 1.2.

Стандарт IEEE 1284 определяет три типа используемых разъемов. Типы A (DB-25) и В (Centronics-36) используются в традиционных кабелях подключения принтера, тип С - новый малогабаритный 36-контактный разъем.

Рис. 1.2. Оконечные цепи линий интерфейса IEEE 1284:

а - однонаправленных, б - двунаправленных

Традиционные интерфейсные кабели имеют от 18 до 25 проводов, в зависимости от числа проводников цепи GND. Эти проводники могут быть как перевитыми, так и нет. К экранированию кабеля жестких требований не предъявлялось. Такие кабели вряд ли будут надежно работать на скорости передачи 2 Мбайт/с и при длине более 2 м. Стандарт IEEE 1284 регламентирует свойства кабелей. Все сигнальные линии должны быть перевитыми с отдельными обратными (общими) проводами.

- Каждая пара должна иметь импеданс 62±б Ом в частотном диапазоне 4-16 МГц.

- Уровень перекрестных помех между парами не должен превышать 10%.

- Кабель должен иметь экран (фольгу), покрывающий не менее 85% внешней поверхности. На концах кабеля экран должен быть окольцован и соединен с контактом разъема.

Кабели, удовлетворяющие этим требованиям, маркируются надписью "lEEEStd 1284-1994 Compliant". Они могут иметь длину до 10 метров, обозначения типов приведены в табл. 1.3.

1.2.2. Режимы передачи данных

IEEE 1284 определяет пять режимов обмена, один из которых полностью соответствует стандартному выводу по протоколу Centronics. Стандарт определяет способ, по которому ПО может определить режим, доступный и хосту (PC), и ПУ (или присоединенному второму компьютеру). Режимы нестандартных портов, реализующих протокол обмена Centronics аппаратно (Fast Centronics, Parallel Port FIFO Mode), могут и не являться режимами IEEE 1284, несмотря на наличие в них черт ЕРР и ЕСР.

При описании режимов обмена фигурируют следующие понятия:

- Хост - компьютер, обладающий параллельным портом.

- ПУ - периферийное устройство, подключаемое к этому порту.

- Ptr - в обозначениях сигналов обозначает передающее ПУ.

- Прямой канал - канал вывода данных от хоста в ПУ.

- Обратный канал - канал ввода данных в хост из ПУ.

Полубайтный режим ввода - Nibble Mode

Предназначен для двунаправленного обмена. Может работать на всех стандартных портах. Порты имеют 5 линий ввода состояния, используя которые ПУ может посылать в хост байт тетрадами (nibble - полубайт, 4 бита) за два приема. Сигнал Ack#, вызывающий прерывание, которое может использоваться в данном режиме, соответствует биту 6 регистра состояния, что усложняет программные манипуляции с битами при сборке байта. Сигналы порта приведены в табл. 1.4, временные диаграммы - на рис. 1.3.

Рис. 1.3. Прием данных в полубайтном режиме

Прием байта данных в полубайтном режиме состоит из следующих фаз:

- ПУ в ответ помещает тетраду на входные линии состояния.

- ПУ сигнализирует о готовности тетрады установкой низкого уровня на линии PtrClk.

- Хост устанавливает высокий уровень на линии HostBusy, указывая на занятость приемом и обработкой тетрады.

- Шаги 1-5 повторяются для второй тетрады, после чего ПУ может сигнализировать о наличии данных для хоста (Selekt) и занятости прямого канала (Busy); вызывать прерывание (ACK).

| Контакт | Сигнал SPP | I/O | Бит | Описание |

| 14 | AutoFeed# | O | CR.1\ | HostBusy - сигнал квитирования. Низкий уровень означает готовность к приему тетрады, высокий подтверждает прием тетрады |

| 17 | Selectln# | O | CR.3\ | |

| 10 | Ack# | I | SR.6 | PtrClk. Низкий уровень означает готовность тетрады, высокий - ответ на сигнал HostBusy |

| 11 | Busy | I | SR.7 | Прием бита данных 3, затем бита 7 |

| 12 | РЕ | I | SR.5 | Прием бита данных 2, затем бита 6 |

| 13 | Sdect | I | SR.4 | Прием бита данных 1, затем бита 5 |

| 15 | Error# | I | SR.3 | Прием бита данных 0, затем бита 4 |

Полубайтный режим сильно нагружает процессор, так как сигналы CR и SR формируются программно, и поэтому поднять скорость обмена выше 50 Кбайт/с не удается. Безусловное его преимущество в том, что он работает на всех портах. Его применяют в тех случаях, когда поток данных невелик (например, для связи с принтерами). Однако при связи с адаптерами локальных сетей, внешними дисковыми накопителями и CD-ROM прием больших объемов данных требует изрядного терпения со стороны пользователя.

Двунаправленный байтный режим - Byte Mode

В данном режиме данные принимаются с использованием двунаправленного порта, у которого выходной буфер данных может отключаться установкой бита С/?.5=1. Как и предыдущие, режим является программно-управляемым - все сигналы квитирования анализируются и устанавливаются драйвером. Сигналы порта описаны в табл. 1.5, временные диаграммы - на рис. 1.4.

| Контакт | Сигнал SPP | Имя в байтном режиме | I/O | Бит | Описание |

| 1 | Strobe# | HostClk | O | CR.0\ | Импульс (низкого уровня) подтверждает прием байта в конце каждого цикла |

| 14 | AutoFeed# | HostBusy | O | CR.1\ | Сигнал квитирования. Низкий уровень означает готовность хоста принять байт; высокий уровень устанавливается по приему байта |

| 17 | Selectln# | 1284Active | O | CR.3\ | Высокий уровень указывает на обмен в режиме IEEE 1284 (в режиме SPP уровень низкий) |

| 16 | Init# | Init# | O | CR.2 | Не используется; установлен высокий уровень |

| 10 | Ack# | PtrClk | I | SR.6 | Устанавливается в низкий уровень для индикации действительности данных на линиях Data . Низкий уровень устанавливается в ответ на сигнал HostBusy |

| 11 | Busy | PtrBusy | I | SR.7\ | Состояние занятости прямого канала |

| 12 | PE | AckDataReq* | 1 | SR.5 | |

| 13 | Select | Xflag* | I | SR.4 | Флаг расширяемости |

| 15 | Error# | DataAvail#* | I | SR.2 | Устанавливается ПУ для указания на наличие обратного канала передачи |

| 2-9 | Data | Data | I/O | DR | Двунаправленный (прямой и обратный) канал данных |

Рис. 1.4. Прием данных в байтном режиме

Фазы приема байта данных:

- Хост сигнализирует о готовности приема данных установкой низкого уровня на линии HostBusy.

- ПУ в ответ помещает байт данных на линии Data .

- ПУ сигнализирует о действительности байта установкой низкого уровня на линии PtrClk.

- Хост устанавливает высокий уровень на линии HostBusy, указывая на занятость приемом и обработкой байта.

- ПУ отвечает установкой высокого уровня на линии PtrClk.

- Хост подтверждает прием байта импульсом HostClk.

- Шаги 1-6 повторяются для каждого следующего байта.

Побайтный режим позволяет поднять скорость обратного канала до скорости прямого канала в стандартном режиме. Однако он может работать только на двунаправленных портах.

Режим ЕРР

Протокол ЕРР (Enhanced Parallel Port - улучшенный параллельный порт) был разработан компаниями Intel, Xircom и Zenith Data Systems задолго до принятия IEEE 1284. Он предназначен для повышения производительности обмена по параллельному порту. ЕРР был реализован в чипсете Intel 386SL (микросхема 82360) и впоследствии принят множеством компаний как дополнительный протокол параллельного порта. Версии протокола, реализованные до принятия IEEE 1284, отличаются от нынешнего стандарта (см. далее).

Протокол ЕРР обеспечивает четыре типа циклов обмена:

- запись данных;

- чтение данных;

- запись адреса;

- чтение адреса.

Назначение циклов записи и чтения данных очевидно. Адресные циклы используются для передачи адресной, канальной и управляющей информации. Циклы обмена данными отличаются от адресных циклов применяемыми стробирующими сигналами. Назначение сигналов порта ЕРР и их связь с сигналами SPP объясняются в табл. 1.6.

| Контакт | Сигнал SPP | Имя в ЕРР | I/O | Описание |

| 1 | Strobe" | Write# | O | Низкий уровень - цикл записи, высокий - цикл чтения |

| 14 | AutoLF# | DataStb# | O | Строб данных. Низкий уровень устанавливается в циклах передачи данных |

| 17 | Selecting | AddrStbft | O | Строб адреса. Низкий уровень устанавливается в адресных циклах |

| 16 | Init# | Reset# | O | Сброс (низким уровнем ПУ переводится в режим совместимости) |

| 10 | Ack# | INTR# | I | Прерывание от ПУ |

| 11 | Busy | Wait# | I | Сигнал квитирования. Низкий уровень разрешает начало цикла (установку строба в низкий уровень), переход в высокий - разрешает завершение цикла (снятие строба) |

| 2-9 | Data | AD | I/O | Двунаправленная шина адреса/данных |

| 12 | PaperEnd | AckDataReq* | I | |

| 13 | Select | Xflag* | I | Используется по усмотрению разработчика периферии |

| 15 | Error# | DataAvail#* | I | Используется по усмотрению разработчика периферии |

ЕРР-порт имеет расширенный набор регистров (табл. 1.7), который занимает в пространстве ввода/вывода 5-8 смежных байт.

| Имя регистра | Смещение | Режим | R/W | Описание |

| SPP Data Port | +0 | SPP/EPP | W | Регистр данных SPP |

| SPP Status Port | +1 | SPP/EPP | R | Регистр состояния SPP |

| SPP Control Port | +2 | SPP/EPP | W | Регистр управления SPP |

| EPP Address Port | +3 | EPP | R/W | Регистр адреса EPP. Чтение или запись в него генерирует связанный цикл чтения или записи адреса EPP |

| EPP Data Port | +4 | EPP | R/W | Регистр данных EPP. Чтение (запись) генерирует связанный цикл чтения (записи) данных EPP |

| Not Defined | +5...+7 | EPP | N/A | В некоторых контроллерах могут использоваться для 16-/32-битных операций ввода/вывода |

В отличие от программно-управляемых режимов, описанных ранее, внешние сигналы EPP-порта для каждого цикла обмена формируются аппаратно по одной операции записи или чтения в регистр порта. На рис. 1.5 приведена диаграмма цикла записи данных, иллюстрирующая внешний цикл обмена, вложенный в цикл записи системной шины процессора (иногда эти циклы называют связанными). Адресный цикл записи отличается от цикла данных только стробом внешнего интерфейса.

Цикл записи данных состоит из следующих фаз:

- Программа выполняет цикл вывода (IOWR#) в порт 4 (EPP Data Port).

- Адаптер устанавливает сигнал Write* (низкий уровень), и данные помещаются на выходную шину LPT-порта.

- При низком уровне Wait# устанавливается строб данных.

- Порт ждет подтверждения от ПУ (перевода Wait# в высокий уровень).

- Снимается строб данных - внешний ЕРР-цикл завершается.

- Завершается процессорный цикл вывода.

- ПУ устанавливает низкий уровень Wait#, указывая на возможность начала следующего цикла.

Рис. 1.5. Цикл записи данных ЕРР

Пример адресного цикла чтения приведен на рис. 1.6. Цикл чтения данных отличается только применением другого стробирующего сигнала.

Рис. 1.6. Адресный цикл чтения ЕРР

Естественно, ПУ не должно "подвешивать" процессор на шинном цикле обмена. Это гарантирует механизм тайм-аутов PC, который принудительно завершает любой цикл обмена, длящийся более 15 мкс. В ряде реализации ЕРР за тайм-аутом интерфейса следит сам адаптер - если ПУ не отвечает в течение определенного времени (5 мкс), цикл прекращается и в дополнительном (не стандартизованном) регистре состояния адаптера фиксируется ошибка.

Устройства с интерфейсом ЕРР, разработанные до принятия IEEE 1284, отличаются началом цикла: строб DataStb# или AddrStb# устанавливается независимо от состояния WAIT#. Это означает, что ПУ не может задержать начало следующего цикла (хотя может растянуть его на требуемое время). Такая спецификация называется ЕРР 1.7 (предложена Xircom). Именно она применялась в контроллере 82360. Периферия, совместимая с ЕРР 17, будет нормально работать и с контроллером ЕРР 1284, но периферия в стандарте ЕРР 1284 может отказаться работать с контроллером ЕРР 1.7.

С программной точки зрения контроллер EРР-порта выглядит просто (см. табл. 1.7). К трем регистрам стандартного порта, имеющим смещение 0, 1 и 2 относительно базового адреса порта, добавлены два регистра (ЕРР Address Port и ЕРР Data Port), чтение и запись в которые вызывает генерацию связанных внешних циклов.

Назначение регистров стандартного порта сохранено для совместимости fPP-порта с ПУ и ПО, рассчитанными на применение программно-управляемого обмена. Поскольку сигналы квитирования адаптером вырабатываются аппаратно, при записи в регистр управления СП биты 0, 1 и 3, соответствующие сигналам Strobeft, AutoFeed# и Selecting должны иметь нулевые значения. Программное вмешательство могло бы нарушить последовательность квитирования. Некоторые адаптеры имеют специальные средства защиты (ЕРР Protect), при включении которых программная модификация этих бит блокируется.

Использование регистра данных ЕРР позволяет осуществлять передачу блока данных с помощью одной инструкции REP INSB или REP OUTSB. Некоторые адаптеры допускают 16-/ 32-битное обращение к регистру данных ЕРР. При этом адаптер просто дешифрует адрес со смещением в диапазоне 4-7 как адрес регистра данных ЕРР, но процессору сообщает о разрядности 8 бит. Тогда 16- или 32-битное обращение по адресу регистра данных ЕРР приведет к автоматической генерации двух или четырех шинных циклов по нарастающим адресам, начиная со смещения 4. Эти циклы будут выполняться быстрее, чем то же количество одиночных циклов. Таким образом обеспечивается производительность до 2 Мбайт/с, достаточная для адаптеров локальных сетей, внешних дисков, стриммеров и CD-ROM. Адресные циклы ЕРР всегда выполняются только в однобайтном режиме.

Важной чертой ЕРР является то, что обращение процессора к ПУ осуществляется в реальном времени - нет буферизации. Драйвер способен отслеживать состояние и подавать команды в точно известные моменты времени. Циклы чтения и записи могут чередоваться в произвольном порядке или идти блоками. Такой тип обмена удобен для регистроориентированных ПУ или ПУ, работающих в реальном времени, - сетевых адаптеров, устройств сбора информации и управления и т. п.

Режим ЕСР

Протокол ЕСР (Extended Capability Port - порт с расширенными возможностями) был предложен Hewlett Packard и Microsoft для связи с ПУ типа принтеров или сканеров. Как и ЕРР, данный протокол обеспечивает высокопроизводительный двунаправленный обмен данными хоста с ПУ.

Протокол ЕСР в обоих направлениях обеспечивает два типа циклов:

- циклы записи и чтения данных;

- командные циклы записи и чтения.

Командные циклы подразделяются на два типа: передачу канальных адресов и передачу счетчика RLC (Run-Length Count).

В отличие от ЕРР, вместе с протоколом ЕСР сразу появился стандарт на программную (регистровую) модель его адаптера, изложенный в документе "The IEEE 1284 Extended Capabilities Port Protocol and ISA Interface Standard" компании Microsoft. Этот документ определяет свойства протокола, не заданные стандартом IEEE 1284:

- компрессию данных хост-адаптером по методу RLE;

- буферизацию FIFO для прямого и обратного каналов;

- применение DMA и программного ввода/вывода.

Компрессия в реальном времени по методу RLE (Run-Length Encoding) позволяет достичь коэффициента сжатия 64:1 при передаче растровых изображений, которые имеют длинные строки повторяющихся байт. Компрессию можно использовать, только если ее поддерживает и хост, и ПУ.

Канальная адресация ЕСР применяется для адресации множества логических устройств, входящих в одно физическое. Например, в комбинированном устройстве факс/принтер/модем, подключаемом только к одному параллельному порту, возможен одновременный прием факса и печать на принтере. В режиме SPP, если принтер установит сигнал занятости, канал будет занят данными, пока принтер их не примет. В режиме ЕСР программный драйвер просто адресуется к другому логическому каналу того же порта.

Протокол ЕСР переопределяет сигналы SPP (табл. 1.8).

| Контакт | Сигнал SPP | Имя в ЕСР | I/O | Описание |

| 1 | Strobe# | HostClk | O | Используется в паре с PeriphAck для передачи в прямом направлении (вывод) |

| 14 | AutoLF# | HostAck | O | Указывает тип цикла (команда/данные) при передаче в прямом направлении. Используется в паре с PeriphClk для передачи в обратном направлении |

| 17 | Selecting | 1284Active | O | Высокий уровень указывает на обмен в режиме IEEE 1284 (в режиме SPP уровень низкий) |

| 16 | Init# | ReverseRequest* | O | Низкий уровень переключает канал на передачу в обратном направлении |

| 10 | Ack# | PeriphQk | I | Используется в паре с HostAck для передачи в обратном направлении |

| 11 | Busy | PeriphAck | I | Используется в паре с HostClk для передачи в обратном направлении. Индицирует тип команда/ данные при передаче в обратном направлении |

| 12 | PaperEnd | AckReverse# | I | Переводится в низкий уровень как подтверждение сигналу ReverseRequest# |

| 13 | Select | Xflag* | I | Флаг расширяемости |

| 15 | Error# | PeriphRequest#* | I | Устанавливается ПУ для указания на доступность (наличие) обратного канала передачи* |

| 2-9 | Data | Data | I/O | Двунаправленный канал данных |

Адаптер ЕСР тоже генерирует внешние протокольные сигналы квитирования аппаратно, но его работа существенно отличается от режима ЕРР.

На рис. 1.7а приведена диаграмма двух циклов прямой передачи: за циклом данных следует командный цикл. Тип цлкла задается уровнем на линии HostAck: в цикле данных - высокий, в командном цикле - низкий. В командном цикле байт может содержать канальный адрес или счетчик RLE. Отличительным признаком является бит 7 (старший): если он нулевой, то биты 0-6 содержат счетчик RLE (0-127), если единичный - то канальный адрес. На рис. 1.76 показана пара циклов обратной передачи.

Рис. 1.7. Передача в режиме ЕСР: a - прямая, б - обратная

В отличие от диаграмм обмена ЕРР, на рис. 1.7 не приведены сигналы циклов системной шины процессора. В данном режиме обмен программы с ПУ разбивается на два относительно независимых процесса, которые связаны через FIFO буфер. Обмен драйвера с FIFO-буфером может осуществляться с использованием как DMA, так и программного ввода-вывода. Обмен ПУ с буфером аппаратно выполняет адаптер ЕСР. Драйвер в режиме ЕСР не имеет информации о точном состоянии процесса обмена, но здесь обычно важно только то, завершен он или нет.

Прямая передача данных на внешнем интерфейсе состоит из следующих шагов:

- Хост помещает данные на шину канала и устанавливает признак цикла данных (высокий уровень) или команды (низкий уровень) на линии HostAck.

- Хост устанавливает низкий уровень на линии HostClk, указывая на действительность данных.

- ПУ отвечает установкой высокого уровня на линии PeriphAck.

- Хост устанавливает высокий уровень линии HostClk, и этот перепад может использоваться для фиксации данных в ПУ.

- ПУ устанавливает низкий уровень на линии PeriphAck для указания на готовность к приему следующего байта.

Поскольку передача в ЕСР происходит через FIFO-буферы, которые могут присутствовать на обеих сторонах интерфейса, важно понимать, на каком этапе данные можно считать переданными. Данные считаются переданными на шаге 4, когда линия HostClk переходит в высокий уровень. В этот момент модифицируются счетчики переданных и принятых байт. В протоколе ЕСР есть условия, вызывающие прекращение обмена между шагами 3 и 4. Тогда эти данные не должны рассматриваться как переданные.

Из рис. 1.7 видно и другое отличие ЕСР от ЕРР. Протокол ЕРР позволяет драйверу чередовать циклы прямой и обратной передачи, не запрашивая подтверждения на смену направления. В ЕСР смена направления должна быть согласована: хост запрашивает реверс установкой ReverseRequest#, после чего он должен дождаться подтверждения сигналом AckReverse#. Поскольку предыдущий цикл мог выполняться по прямому доступу, драйвер должен дождаться завершения прямого доступа или прервать его, выгрузить буфер FIFO, определив точное значение счетчика переданных байт, и только после этого запрашивать реверс.

Обратная передача данных состоит из следующих шагов:

- Хост запрашивает изменение направления канала, устанавливая низкий уровень на линии ReverseRequest#.

- ПУ разрешает смену направления установкой низкого уровня на линии AckReverse#.

- ПУ помещает данные на шину канала и устанавливает признак цикла данных (высокий уровень) или команды (низкий уровень) на линии PeriphAck.

- ПУ устанавливает низкий уровень на линии PeriphClk, указывая на действительность данных.

- Хост отвечает установкой высокого уровня на линии HostAck.

- ПУ устанавливает высокий уровень линии PeriphClk; этот перепад может использоваться для фиксации данных хостом.

- Хост устанавливает низкий уровень на линии HostAck для указания на готовность к приему следующего байта.

Режимы и регистры ЕСР - порта *

* Этот режим не входит в спецификацию Microsoft, но трактуется как EPP контроллером SMC FDC37C665/666 и многими другими.

Программный интерфейс и регистры ЕСР для адаптеров IEEE 1284 определяет спецификация Microsoft. Определены режимы (табл. 1.9), в которых может функционировать адаптер. Они задаются полем Mode регистра ECR (биты ).

Регистровая модель адаптера ЕСР (табл. 1.10) использует свойства архитектуры стандартной шины и адаптеров ISA - для дешифрации адресов портов ввода/вывода задействуются только 10 младших линий шины адреса. Поэтому, например, обращения по адресам Port, Port+400h, Port+800h... будут восприниматься как обращения к адресу Port, лежащему в диапазоне 0-3FFh. Современные PC и адаптеры декодируют большее количество адресных бит, поэтому обращения по адресам 0378h и 0778h будет адресованы двум различным регистрам. Помещение дополнительных регистров ЕСР "за спину" регистров стандартного порта (смещение 400-402h) преследует две цели. Во-первых, эти адреса никогда не использовались традиционными адаптерами и их драйверами, и их применение в ЕСР не приведет к сужению доступного адресного пространства ввода/вывода. Во-вторых, этим обеспечивается совместимость со старыми адаптерами на уровне режимов 000-001 и возможность определения присутствия EСР - адаптера через попытку обращения к его расширенным регистрам.

| Режим | Название | Описание |

| 000 | SPPmode | Стандартный (традиционный) режим |

| 001 | Bi-directional mode | Двунаправленный порт (тип 1 для PS/2) |

| 010 | Fast Centronics | Однонаправленный с использованием FIFO и DMA |

| 011 | ECP Parallel Port mode | ECP |

| 100 | EPP Parallel Port mode* | Перевод в режим EPP |

| 101 | Зарезервировано | - |

| 110 | Test mode | Тестирование работы FIFO и прерываний |

| 111 | Configuration mode | Доступ к конфигурационным регистрам |

Каждому режиму ECP соответствуют (и доступны) свои функциональные регистры. Переключение режимов осуществляется записью в регистр ECR. "Дежурными" режимами, включаемыми по умолчанию, являются 000 или 001. В любом из них работает полубайтный режим ввода. Из этих режимов всегда можно переключиться в любой другой, но из старших режимов (010-111) переключение возможно только в 000 или 001. Для корректной работы интерфейса перед выходом из старших режимов необходимо дождаться завершения обмена по прямому доступу и очистки FIFO-буфера.

В режиме 000 (SPP) порт работает как стандартный однонаправленный программно-управляемый SPP.

В режиме 001 (Bi-Di PS/2) порт работает как двунаправленный порт PS/2 типа 1. От режима 000 отличается возможностью реверса канала данных по биту CR.5.

Режим 010(Fast Centronics) предназначен только для высокопроизводительного вывода через FIFO-буфер с использованием DMA. Сигналы квитирования по протоколу Ceritromcs вырабатываются аппаратно. Сигнал запроса прерывания вырабатывается по состоянию FIFO-буфера, но не по сигналу Аск# (запрос одиночного байта "не интересует" драйвер быстрого блочного вывода).

Режим 011 является собственно режимом ЕСР, описанным ранее. Поток данных и команд, передаваемых в ПУ, помещается в FIFO-буфер через регистры ECPDFIFO и ECPAFIFO соответственно. Из FIFO они выводятся с соответствующим признаком цикла (состояние линии HostAck). Принимаемый поток данных от ПУ извлекается из FIFO-буфера через регистр ECPDFIFO. Получение адреса в командном цикле от ПУ не предусматривается. Обмен с регистром ECPDFIFO может производиться и по каналу DMA.

Компрессия по методу RLE при передаче выполняется программно. Для передачи подряд более двух одинаковых байт данных в регистр ECPAFIFO записывается байт, у которого младшие 7 бит содержат счетчик RLC (значение RLC=127 соответствует 128 повторам), а старший бит нулевой. После этого в ECPDFIFO записывается сам байт. Отсюда очевидно, что вывод данных с одновременным использованием компрессии и DMA невозможен. Принимая эту пару байт (командный байт и байт данных), ПУ осуществляет декомпрессию. При приеме потока от ПУ адаптер ЕСР декомпрессию осуществляет аппаратно и в FIFO-буфер помещает уже декомпрессированные данные.

Режим 100 (ЕРР) - один из способов включения режима ЕРР.

Режим 110 (Test Mode) предназначен для тестирования взаимодействия FIFO и прерываний. Данные могут передаваться в/из регистра TFIFO с помощью DMA или программным способом. На внешний интерфейс обмен не воздействует. Адаптер отрабатывает операции вхолостую на максимальной скорости интерфейса (как будто сигналы квитирования приходят без задержек). Адаптер следит за состоянием буфера и по мере необходимости вырабатывает сигналы запроса прерывания. Таким образом программа может определить максимальную пропускную способность канала.

Режим 111 (Configuration mode) предназначен для доступа к конфигурационным регистрам. Выделение режима защищает адаптер и протокол от некорректных изменений конфигурации в процессе обмена.

| Смещение | Имя | R/W | Режимы ЕСР* | Название |

| 000 | DR | R/W | 000-001 | Data Register |

| 000 | ECPAF1FO | R/W | 011 | ЕСР Address FIFO |

| 001 | SR | R/W | Все | Status Register |

| 002 | CR | R/W | Все | Control Register |

| 400 | SDFIFO | R/W | 010 | Parallel Pwt Data FIFO |

| 400 | ECPDFIFO | R/W | 011 | ЕСР Data FIFO |

| 400 | TFIFO | R/W | 110 | Test FIFO |

| 400 | CNFGA | R | 111 | Configuration Register A |

| 401 | CNFGB | R/W | 111 | Configuration Register В |

| 402 | ECR | R/W | Все | Extended Control Register |

Регистр данных DR используется для передачи данных только в программно-управляемых режимах (000 и 001).

Регистр состояния SR передает значение сигналов на соответствующих линиях (как в SPP ).

Регистр управления CR имеет назначение бит, совпадающее с SPP. В режимах 010, 011 запись в биты 0, 1 (сигналы AutoLF# и Strobe#) игнорируется.

Регистр ECPAFIFO служит для помещения информации командных циклов (канального адреса или счетчика RLE, в зависимости от бита 7) в FIFO-буфер. Из буфера информация будет выдана в командном цикле вывода.

Регистр SDFIFO используется для передачи данных в режиме 010. Данные, записанные в регистр (или посланные по каналу DMA), передаются через буфер FIFO по реализованному аппаратно протоколу Centronics. При этом должно быть задано прямое направление передачи (бит CR.5=0).

Регистр DFIFO используется для обмена данными в режиме 011 (ЕСР). Данные, записанные в регистр или считанные из него (или переданные по каналу DMA), передаются через буфер FIFO по протоколу ЕСР.

Регистр TFIFO обеспечивает механизм тестирования FIFO - буфера в режиме 110.

Регистр ECPCFGA позволяет считывать информацию об адаптере (идентификационный код в битах ).

Регистр ECPCFGB хранит информацию, необходимую драйверу. Запись в регистр не влияет на работу порта.

Регистр ECR - главный управляющий регистр ЕСР.

Назначение бит регистра ECR:

- ECR -ЕСР MODE - задает режим ЕСР.

- ECR.4 - ERRINTREN^t (Error Interrupt Disable) - запрещает прерывания по сигналу Error# (при нулевом значении бита по отрицательному перепаду на этой линии вырабатывается запрос прерывания).

- ECR.3 - DMAEN (DMA Enable) - разрешает обмен по каналу DMA.

- ECR.2 - SERVICEINTR (Service Interrupt) - запрещает сервисные прерывания, которые вырабатываются по окончании цикла DMA (если он разрешен), по порогу заполнения/опустошения FIFO-буфера (если не используется DMA) и по ошибке переполнения буфера сверху или снизу.

- ECR.1 - FIFOFS (FIFO Full Status) - сигнализирует о заполнении буфера; при FIFOFS=1 в буфере нет ни одного свободного байта.

- ECR.0 - FIFOES (FIFO Empty Status) - указывает на полное опустошение буфера; комбинация FIFOFS=FIFOES=i означает ошибку работы с FIFO (переполнение сверху или снизу).

Когда порт находится в стандартном или двунаправленном режимах (000 или 001), первые три регистра полностью совпадают с регистрами стандартного порта. Так обеспечивается совместимость драйвера со старыми адаптерами и старых драйверов с новыми адаптерами.

По интерфейсу с программой ECP-порт напоминает ЕРР: после установки режима (записи кода в регистр ECR) обмен данными с устройством сводится к чтению или записи в соответствующие регистры. За состоянием FIFO-буфера наблюдают либо по регистру ECR, либо по обслуживанию сервисных прерываний от порта. Весь протокол квитирования генерируется адаптером аппаратно. Обмен данными с ЕСР - портом (кроме явного программного) возможен и по прямому доступу к памяти (каналу DMA), что эффективно при передаче больших блоков данных.

1.2.3. Согласование режимов IEEE 1284

ПУ в стандарте IEEE 1284 обычно не требуют от контроллера реализации всех режимов, предусмотренных стандартом. Для определения режимов и методов управления конкретным устройством стандарт предусматривает последовательность согласования (negotiation sequence). Последовательность построена так, что старые устройства, не рассчитанные на применение IEEE 1284, на нее не ответят, и контроллер останется в стандартном режиме. Периферия IEEE 1284 может сообщить о своих возможностях, и контроллер установит режим, удовлетворяющий и хост, и ПУ.

Во время фазы согласования контроллер выставляет на линии данных байт расширяемости (extensibility byte), запрашивая подтверждение на перевод интерфейса в требуемый режим или прием идентификатора ПУ (табл. 1.11). Идентификатор передается контроллеру в запрошенном режиме (любой режим обратного канала, кроме ЕРР). ПУ использует сигнал Xflag (Select в терминах SPP) для подтверждения запрошенного режима обратного канала, кроме полубайтного. Полубайтный режим поддерживается всеми устройствами IEEE 1284. Бит Extensibility Link request послужит для определения дополнительных режимов в будущих расширениях стандарта.

| Бит | Описание | Допустимые комбинации бит |

| 7 | Request Extensibility Link - зарезервирован | 10000000 |

| 6 | Запрос режима ЕРР | 01000000 |

| 5 | Запрос режима ЕСР с RLE | 00110000 |

| 4 | Запрос режима ЕСР без RLE | 00010000 |

| 3 | Зарезервировано | 00001000 |

| 2 | Запрос идентификатора устройства с ответом в режиме: | |

| полубайтный | 00000100 | |

| байтный | 00000101 | |

| ЕСР без RLE | 00010100 | |

| ЕСР с RLE | 0011 0100 | |

| 1 | Зарезервировано | 00000010 |

| 0 | Запрос полубайтного режима | 00000001 |

| none | Запрос байтного режима | 00000000 |

Последовательность согласования (рис. 1.8) состоит из следующих шагов:

- Хост выводит байт расширяемости на линии данных.

- Хост устанавливает высокий уровень сигнала Selecting и низкий - AutoFeed#, что означает начало последовательности согласования.

- ПУ отвечает установкой низкого уровня сигнала Ack# и высокого - Errorft, PaperEnd и Select. Устройство, "не понимающее" стандарта 1284, ответа не даст, и дальнейшие шаги не выполнятся.

- Хост устанавливает низкий уровень сигнала Strobe# для записи байта расширяемости в ПУ.

- Хост устанавливает высокий уровень сигналов Strobeft и AutoLF#.

- ПУ отвечает установкой в низкий уровень сигналов PaperEnd и Еггог^, если ПУ имеет обратный канал передачи данных. Если запрошенный режим поддерживается устройством, на линии Select устанавливается высокий уровень, если не поддерживается - низкий.

- ПУ устанавливает высокий уровень на линии Ack# для указания на завершение последовательности согласования, после чего контроллер устанавливает требуемый режим работы.

Рис. 1.8. Последовательность согласования режимов IEEE 1284

1.2.4. Развитие стандарта IEEE 1284

Кроме основного стандарта IEEE 1284, который уже принят, в настоящее время в стадии проработки находятся новые стандарты, дополняющие его. К ним относятся:

- IEEE Р1284.1 "Standard for Information Technology for Transport Independent Printer/ Scanner Interface (TIP/SI)". Этот стандарт разрабатывается для управления и обслуживания сканеров и принтеров на основе протокола NPAP (Network Printing Alliance Protocol).

- IEEE P1284.2 "Standard for Test, Measurement and Conformance to IEEE Std. 1284" - стандарт для тестирования портов, кабелей и устройств на совместимость с IEEE 1284.

- IEEE P12843 "Standard for Interface and Protocol Extensions to IEEE Std. 1284 Compliant Peripheral and Host Adapter Ports" - стандарт на драйверы и использование устройств прикладным программным обеспечением (ПО). Уже приняты спецификации BIOS для использования ЕРР драйверами DOS. Прорабатывается стандарт на разделяемое использование одного порта цепочкой устройств или группой устройств, подключаемых через мультиплексор.

- IEEE P1284.4 "Standard for Data Delivery and Logical Channels for IEEE Std. 1284 Interfaces" направлен на реализацию пакетного протокола достоверной передачи данных через параллельный порт. Основой служит протокол MLC (Multiple Logical Channels) фирмы Hewlett- Packard, однако совместимость с ним в окончательной версии стандарта не гарантируется.

1.3. Применение параллельных интерфейсов и LPT-портов

Параллельные интерфейсы применяются в компьютерах разных семейств и классов, здесь мы ограничимся рассмотрением IBM PC-совместимых компьютеров.

1.3.1. Использование параллельных интерфейсов

Распространенным применением LPT-порта является подключение принтера и плоттера. Остановимся на аппаратных аспектах - режиме порта и кабеле подключения. Практически все принтеры могут работать с портом в режиме SPP, но применение расширенных режимов дает свои преимущества:

- Двунаправленный режим (Bi-Di) не повышает производительность, но служит для сообщения о состоянии и параметрах принтера.

- Скоростные режимы (Fast Centronics) повышают производительность принтера, но могут потребовать качественного кабеля (см. далее). От принтера не требуется каких-либо дополнительных "интеллектуальных" способностей.

- Режим ЕСР - потенциально самый эффективный, имеет системную поддержку во всех версиях Windows. На некоторых принтерах реализован не полностью (может отсутствовать аппаратная компрессия). ЕСР поддерживают принтеры HP DeskJet моделей бхх, LaserJet 4 и далее, современные модели фирмы Lexmark. Требует применения кабеля, по частотным свойствам соответствующего IEEE 1284.

Простейший вариант кабеля подключения принтера - 18-проводный кабель с неперевитыми проводами. Он используется для работы в режиме SPP. При длине более 2 м желательно, чтобы хотя бы линии Strobe# и Busy были перевиты с отдельными общими проводами. Для скоростных режимов может оказаться непригодным, причем сбои могут происходить нерегулярно и лишь при определенных последовательностях передаваемых кодов. Встречаются кабели Centronics, у которых отсутствует связь контакта 17 разъема PC с контактом 36 разъема принтера. При попытке подключения таким кабелем принтера, работающего в стандарте 1284, появится сообщение о необходимости применения "двунаправленного кабеля". Принтер не может сообщить системе о поддержке расширенных режимов, на что рассчитывают драйверы принтера.

Неплохие электрические свойства имеют ленточные кабели, у которых сигнальные цепи (управляющих сигналов) чередуются с общими проводами. Но их применение в качестве внешнего интерфейса непрактично (нет второго защитного слоя изоляции, высокая уязвимость) и неэстетично (круглые кабели смотрятся лучше).

Идеальным вариантом являются кабели, в которых все сигнальные линии перевиты с общими проводами и заключены в общий экран - то, что требует IEEE 1248. Такие кабели гарантированно работают на скоростях до 2 Мбайт/с, их длина может достигать 10 м.

В табл. 1.12 приводится распайка кабеля подключения принтера с разъемом XI типа A (DB25-P) со стороны PC и Х2 типа В (Centronics-36) или типа С (миниатюрный) со стороны принтера. Использование общих проводов (GND) зависит от качества кабеля (см. выше). В простейшем случае (18-проводный кабель) все сигналы GND объединяются в один провод. Качественные кабели требуют отдельного обратного провода для каждой сигнальной линии, однако в разъемах типа А и В для этого недостаточно контактов (см. табл. 1.12, где в скобках указаны номера контактов разъема PC типа А, которым соответствуют обратные провода). В разъеме типа С обратный провод (GND) имеется для каждой сигнальной цепи; сигнальным контактам 1-17 этого разъема соответствуют контакты GND 19-35.

| XI,разъем PC типа А | Сигнал | Х2, разъем PRN типа В | Х2, разъем PRN типа С |

| 1 | Strobe# | 1 | 15 |

| 2 | Data 0 | 2 | 6 |

| 3 | Data 1 | 3 | 7 |

| 4 | Data 2 | 4 | 8 |

| 5 | Data 3 | 5 | 9 |

| 6 | Data 4 | 6 | 10 |

| 7 | Data 5 | 7 | 11 |

| 8 | Data 6 | 8 | 12 |

| 9 | Data7 | 9 | 13 |

| 10 | Ack# | 10 | 3 |

| 11 | Busy | 11 | 1 |

| 12 | PaperEnd | 12 | 5 |

| 13 | Select | 13 | 2 |

| 14 | AutoLF# | 14 | 17 |

| 15 | Error* | 32 | 4 |

| 16 | lnit# | 31 | 14 |

| 17 | Selecting | 36 | 16 |

| 18 | GND(1) | 19 | 33 |

| 19 | GND (2 3) | 20 21 | 24 25 |

| 20 | GND (4 5) | 22 23 | 26 27 |

| 21 | GND (6 7) | 24 25 | 28 29 |

| 22 | GND (8 9) | 26 27 | 30 31 |

| 23 | GND (11 15) | 29 | 19 22 |

| 24 | GND (10 12 13) | 28 | 20 21 23 |

| 25 | GND (14 16 17) | 30 | 32 34 35 |

Ряд отечественных (и стран бывшего СЭВ) принтеров имеет интерфейс ИРПР (IFSP в документации на принтеры ROBOTRON). Он является близким родственником интерфейса Centronics, но со следующими отличиями:

- Линии данных инвертированы. Протокол квитирования несколько иной.

- Ко всем входным линиям (на принтере) подключены пары согласующих резисторов: 220 Ом к питанию +5 В и 330 Ом к общему проводу. Это позволяет использовать длинные кабели, но перегружает большинство интерфейсных адаптеров PC.

- Сигналы ошибки и конца бумаги отсутствуют.

Интерфейс ИРПР может быть программно реализован через обычный LPT-порт, но для устранения перегрузки выходных линий согласующие резисторы из принтера желательно удалить. Порт, перегруженный по выходу, может преподносить всякого рода сюрпризы (естественно, неприятные и трудно диагностируемые).

Для связи двух компьютеров по параллельному интерфейсу применяются различные кабели в зависимости от режимов используемых портов. Самый простой и медленный - полубайтный режим, работающий на всех портах. Для этого режима в кабеле достаточно иметь 10 сигнальных и один общий провод. Распайка разъемов кабеля приведена в табл. 1.13. Связь двух PC данным кабелем поддерживается стандартным ПО типа Interink из MS-DOS или Norton Commander.

Для машин PS/2 с двунаправленным портом фирма IBM выпускала переходное устройство в комплекте с программой Data Migration Facility. Переходник устанавливался на разъем LPT-порта PS/2, а к его разъему Х2 типа Centronics присоединялся обычный принтерный кабель, подключаемый к LPT-порту любого PC. Так предлагалось решить проблему переноса файлов со старых компьютеров, оснащенных 5" дисководами, на компьютеры PS/2 с дисководами 3,5". Распайка такого переходника приведена в табл. 1.14. Как видно, данный переходник нельзя использовать при связи через Interink или Norton Commander. Если обе соединяемые машины имеют двунаправленные порты, переходник обеспечивает симметричную двунаправленную связь. По скорости обмена превосходит вышеописанное полубайтное соединение в 2 раза. Это соединение не соответствует двунаправленному режиму IEEE 1284.

| XI, разъем РС#1 | Х2, разъем РС#2 | ||

| Бит | Контакт | Контакт | Бит |

| DR.O | 2 | 15 | SR.3 |

| DR.1 | 3 | 13 | SR.4 |

| DR.2 | 4 | 12 | SR.5 |

| DR.3 | 5 | 10 | SR.6 |

| DR.4 | 6 | 11 | SR.7 |

| SR.6 | 10 | 5 | DR.3 |

| SR.7 | 11 | 6 | DR.4 |

| SR.5 | 12 | 4 | DR.2 |

| SR.4 | 13 | 3 | DR.1 |

| SR.3 | 15 | 2 | DR.O |

| GND | 18-25 | 18-25 | GND |

Разъемы XI и Х2 - DB25-P (вилки).

| XI | Х2 | ||

| Контакт | Бит | Бит | Контакт |

| 1 | CR.0 | SR.6 | 10 |

| 2 | DR.0 | DR.0 | 2 |

| 3 | DR.1 | DR.1 | 3 |

| 4 | DR.2 | DR.2 | 4 |

| 5 | DR.3 | DR.3 | 5 |

| 6 | DR.4 | DR.4 | 6 |

| 7 | DR.5 | DR.5 | 7 |

| 8 | DR.6 | DR.6 | 8 |

| 9 | DR.7 | DR.7 | 9 |

| 10 | SR.6 | CR.0 | 1 |

| 12 | SR.5 | CR.3 | 36 |

| 17 | CR.3 | SR.5 | 12 |

| 18-25 | GND | GND | 19-30, 33 |

Разъемы XI - DB25-P (вилка), Х2 - Centmnics-36 (розетка).

Высокоскоростная связь двух компьютеров может выполняться и в режиме ЕСР (режим ЕРР неудобен, поскольку требует синхронизации шинных циклов ввода/вывода двух компьютеров). В табл. 1.15 приведена распайка кабеля. В отличие от предыдущих таблиц, описывающих кабели для программно-управляемых режимов, в ней приведены имена сигналов, которые аппаратно генерируются адаптерами портов. Этот же кабель может использоваться и для связи в байтном режиме. Такая связь поддерживается Windows 95.

| Разъем XI | Разъем Х2 | ||

| Контакт | Имя в ЕСР | Имя в ЕСР | Контакт |

| 1 | HostClk | PeriphClk | 10 |

| 14 | HostAck | PeriphAck | 11 |

| 17 | 1284Active | PeriphRequest# | 15 |

| 16 | ReverseRequest* | AckReverse* | 12 |

| 10 | PeriphClk | HostClk | 1 |

| 11 | PeriphAck | ^MostAck | 14 |

| 12 | AckReverse* | ReverseRequest# | 16 |

| 13 | Xflag | /- | - |

| 15 | PeriphRequest# | 1284Active | 17 |

| 2-9 | Data | Data | 2-9 |

Подключение сканера к LPT-порту эффективно, только если порт обеспечивает хотя бы двунаправленный режим (Bi-Di), поскольку основной поток - ввод. Лучше использовать порт ЕСР, если этот режим поддерживается сканером (или ЕРР, что маловероятно).

Подключение внешних накопителей (lomega Zip Drive, CD-ROM и др.), адаптеров ЛВС и других симметричных устройств ввода/вывода имеет свою специфику. В режиме SPP наряду с замедлением работы устройства заметна принципиальная асимметрия этого режима: чтение данных происходит в два раза медленнее, чем (весьма небыстрая) запись . Применение двунаправленного режима (Bi-Di или PS/2 Type 1} устранит эту асимметрию - скорости сравняются. Только перейдя на ЕРР, можно получить нормальную скорость работы. В режиме ЕРР подключение к LPT-порту почти не уступает по скорости подключению через ISA- контроллер. Это справедливо и при подключении устройств со стандартным интерфейсом шин к LPT-портам через преобразователи интерфейсов (например, LPT - IDE, LPT - SCSI, LPT - PCMCIA).

В табл. 1.16 описано назначение выводов разъема LPT-порта в различных режимах и их соответствие битам регистров стандартного порта.

| Контакт | I/O | Бит* | SPP | ECP | ЕРР |

| 1 | O/I | CR.0\ | Strobe# | Hostdk | Write# |

| 2 | O/I | DR.0 | Data0 | Data0 | Data0 |

| 3 | O/I | DR.1 | Data1 | Data1 | Data1 |

| 4 | O/I | DR.2 | Data2 | Data2 | Data2 |

| 5 | O/I | DR.3 | Data3 | Data3 | Data3 |

| 6 | O/I | DR.4 | Data4 | Data4 | Data4 |

| 7 | O/I | DR.5 | Data5 | Data5 | Data5 |

| 8 | O/I | DR.6 | Data6 | Data6 | Data6 |

| 9 | O/I | DR.7 | Data7 | Data7 | Data7 |

| 10 | I | SR.6 | Ack# | PeriphClk | INTR# |

| 11 | I | SR.7\ | Busy | PeriphAck | Wait" |

| 12 | I | SR.5 | PaperEnd | AckReverse* | ^* |

| 13 | I | SR.4 | Select | Xflag | ** |

| 14 | O/I | CR.1\ | AutoLF# | HostAck | DataStb# |

| 15 | I | SR.3 | Error" | PeriphRequest# | ** |

| 16 | O/I | CR2 | hit" | ReverseRequest* | Reset* |

| 17 | O/I | CR.3\ | Selecting | 1284Active | AddrStb# |

1.3.2. Конфигурирование LPT-портов

Управление параллельным портом разделяется на два этапа - предварительное конфигурирование (Setup) аппаратных средств порта и текущее (оперативное) переключение режимов работы прикладным или системным ПО. Оперативное переключение возможно только в пределах режимов, разрешенных при конфигурировании. Этим обеспечивается возможность согласования аппаратуры с ПО и блокирования ложных переключении, вызванных некорректными действиями программы.

Конфигурирование LPT-порта зависит от его исполнения. Порт, расположенный на плате расширения (мультикарте), устанавливаемой в слот ISA или ISA+VLB, конфигурируется джамперами на самой плате. Порт на системной плате конфигурируется через BIOS Setup.

Конфигурированию подлежат следующие параметры:

- Базовый адрес - 3BCh, 378h или 278h. При инициализации BIOS проверяет наличие портов по адресам именно в этом порядке и, соответственно, присваивает обнаруженным портам логические имена LPT1, LPT2, LPT3. Адрес 3BCh имеет адаптер порта, расположенный на плате MDA или HGC. Большинство портов по умолчанию конфигурируются на адрес 378h и могут переключаться на 278h.

- Используемая линия запроса прерывания: для LPT - IRQ7, для LPT2 - IRQ5. Традиционно прерывания от принтера не используются, и этот дефицитный ресурс можно сэкономить. Однако при использовании скоростных режимов ЕСР (или Fast Centronics) работа через прерывания может заметно повысить производительность и снизить загрузку процессора.

- Использование канала DMA для режимов ЕСР и Fast Centronics - разрешение и номер канала DMA (по умолчанию - 3).

Режимы работы порта:

- SPP - порт работает только в стандартном однонаправленном программно-управляемом режиме. PS/2, он же Bi-Directional - отличается от SPP возможностью реверса канала (установкой СЯ.5=7).

- Fast Centronics - аппаратное формирование протокола Centronics с использованием FIFO-буфера и, возможно, DMA.

- ЕРР - в зависимости от использования регистров порт работает в режиме SPP или ЕРР.

- ЕСР - по умолчанию включается в режим SPP или PS/2, записью в ECR может переводиться в любой режим ЕСР, но перевод в ЕРР записью в ECR кода 100 не гарантируется.

- ЕСР+ЕРР - то же, что и ЕСР, но запись в ECR кода режима 100 переводит порт в ЕРР.

Выбор режима ЕРР, ЕСР или Fast Centronics сам по себе не приводит к повышению быстродействия обмена с подключенными ПУ, а только дает возможность драйверу и ПУ установить оптимальный режим в пределах их "разумения". Большинство современных драйверов и приложений пытаются использовать эффективные режимы, так что "подрезать им крылья" установкой простых режимов без веских оснований не стоит.

Принтеры и сканеры могут пожелать режима ЕСР. Windows (3-х, 95 и NT) имеет системные драйверы для этого режима. В среде DOS печать через ЕСР поддерживается только специальным загружаемым драйвером. Сетевые адаптеры, внешние диски и CD-ROM, подключаемые к параллельному порту, могут использовать режим ЕРР. Для этого режима специальный драйвер пока еще не применяется; использование ЕРР включается в драйвер самого подключаемого устройства.